ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

$4.99

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

Lab 9: Counters, Clock, Dividers, and Debounce Circuits

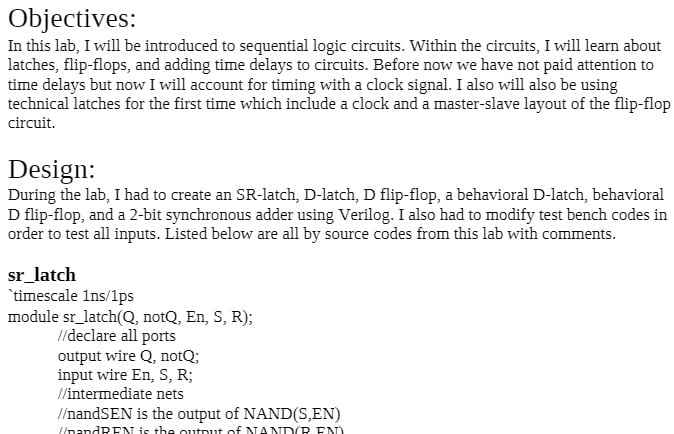

Objectives:

The purpose of this lab is to help reinforce my knowledge of sequential circuits byintroducing an important synchronous sequential circuit, the binary counter, through the binaryup-counter using familiar combinational components as well as sequential components discussedin the previous lab.

This lab will also demonstrate two more important use cases for binarycounters, namely clock frequency division and I/O debouncing, familiarizing me more withdesigns concepts that will be tested on the FPGA board.

Design:

Exp 1

–Create a new project called lab9.

–

Description

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

Lab 9: Counters, Clock, Dividers, and Debounce Circuits

Objectives:

The purpose of this lab is to help reinforce my knowledge of sequential circuits byintroducing an important synchronous sequential circuit, the binary counter, through the binaryup-counter using familiar combinational components as well as sequential components discussedin the previous lab.

This lab will also demonstrate two more important use cases for binarycounters, namely clock frequency division and I/O debouncing, familiarizing me more withdesigns concepts that will be tested on the FPGA board.

Design:

Exp 1

–Create a new project called lab9.

–Type the Verilog code provided into a source file and save it as ‘clock divider.v’–Connect the logic analyzer to the ZYBO board, as well as the initial setup of the logicanalyzer.

–Ensure that the FPGA board is turned off. Then, locate the JB connector towards thebottom-right of the FPGA board. Open the XDC file and compare it to the diagram inFigure 6, and locate the ClkOut signals of the clock divider.

–Examine the end of the cable, taking note of the individual channel labels. Use thebreadboard and jumper wires to connect the all the ‘GND’ ports on channel 0,1,2,3 to the‘GND’ on JB. Now connect channels 0 through 3 to ClkOut[0] through ClkOut[3] on JBin a similar manner. Have the TA inspect the setup before moving on.

–Turn the logic analyzer on.–Press the Digital button on the front panel

–Press the Channel softkey. Check channels from D0 to D3 and uncheck all the otherchannels, using the Entry knob to choose different channels and press the Entry knob tocheck/uncheck

–Press the Label button. Then press the Channel softkey. Turn the Entry knob to move thehighlight cursor to D0:D0 and select it by pressing the Entry knob.

–Press Enter softkey and then press Spell softkey. Use the Entry knob to select and enterCOUNT2 one character by one character in the New label field. Then press Apply NewLabel softkey to assign channel D0 with a COUNT2 label.

–Repeat the same process to assign a COUNT3 label to D1 channel, a COUNT4 label toD2 channel, and a COUNT5 label to D3 channel.

–Press Run on the logic analyzer once the FPGA has been programmed successfully,should see four separate clock signals on the logic analyzer. Press Auto Scale button oruse the Horizontal Knob to adjust the horizontal scale

–Working with the logic analyzer, press the Cursor button. Use the cursors knob to selectand move the X1 and X2 cursors on the screen, and measure the periods of COUNT2,COUNT3, COUNT4, COUNT5

–Press Digital Button, then press Bus softkey then check Bus1. Then press Channelsoftkey and select D0, D1, D2, D3

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 INTRO TO DIGITAL LOGIC School: Texas A&M University (Texas A&M) *Professor:Ivan Diaz Rodriguez, Lu, CHOI, SRINIVAS, SHAKKOTTAI, Staff, K… Documents (2709) Q&A (26) Textbook Exercises (20+) Most important docs of the week 3 pagesLab 1 Post-Lab.docxLab 1 Post-Lab.docx Texas A&M University

ECEN 248 – Fall 2017 Register Now Lab 1 Post-Lab.docx 13 pagesLab Report 12.docxLab Report 12.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab Report 12.docx 13 pagesLab 12 post labLab 12 post lab Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12 post lab 8 pagesLab 12 – Report.docxLab 12 – Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12 – Report.docx 6 pagesLab 12 PreLab.docxLab 12 PreLab.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 – Spring 2014 Register Now Lab 12 PreLab.docx INTRO TO DIGITAL LOGIC Documents All (2709) Homework Help (65) Lab Reports (1350) Lecture Slides (4) Notes (130) Test Prep (61) Showing 1 to 30 of 2,709 Sort by:

Most Popular 8 pagesLab6IntroductiontoLogicSimulationandVerilogLab6IntroductiontoLogicSimulationandVerilog Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab6IntroductiontoLogicSimulationandVerilog 10 pagesLab 8Lab 8 Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now Lab 8 11 pagesECEN_248 Lab9.pdfECEN_248 Lab9.pdf Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2018 Register Now ECEN_248 Lab9.pdf 6 pagesLab 12 PreLab.docxLab 12 PreLab.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12 PreLab.docx 8 pagesECEN 248 lab6ECEN 248 lab6 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2015 Register Now ECEN 248 lab6 8 pagesECEN 248 lab8_reportECEN 248 lab8_report Texas A&M University INTRO TO DIGITAL SYSTEMS DESIGN

ECEN 248 – Fall 2015 Register Now ECEN 248 lab8_report 10 pagesLab9Lab9 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 – Spring 2014 Register Now Lab9 3 pagesprelab11prelab11 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now prelab11 14 pageslab8lab8 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2015 Register Now lab8 10 pagesLab 9 Report.docxLab 9 Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 9 Report.docx 7 pagesLab 9 Report.docxLab 9 Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2008 Register Now Lab 9 Report.docx 6 pagesUntitleddocument (2)Untitleddocument (2) Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now Untitleddocument (2) 2 pagesPreLab 8 Report.docxPreLab 8 Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now PreLab 8 Report.docx 2 pagesENGR 216 LAB 6.docxENGR 216 LAB 6.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now ENGR 216 LAB 6.docx 3 pagesPrelab 7Prelab 7 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 – Fall 2013 Register Now Prelab 7 17 pageslab9_honorslab9_honors Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now lab9_honors 13 pagesLab 12 post labLab 12 post lab Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12 post lab 8 pagesLab 12 – Report.docxLab 12 – Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12 – Report.docx 16 pagesLab 12.docxLab 12.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now Lab 12.docx 7 pagesECEN 248 Lab 7 reportECEN 248 Lab 7 report Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2014 Register Now ECEN 248 Lab 7 report 3 pagesecen 248 Prelab 5ecen 248 Prelab 5 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2014 Register Now ecen 248 Prelab 5 5 pagesprelab 9.docxprelab 9.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now prelab 9.docx 13 pageslab12_regularlab12_regular Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 – Spring 2014 Register Now lab12_regular 6 pagesLAB 3LAB 3 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now LAB 3 6 pagesLab 5 Report.docxLab 5 Report.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2008 Register Now Lab 5 Report.docx 4 pagesECEN 248 Post-Lab 1ECEN 248 Post-Lab 1 Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now ECEN 248 Post-Lab 1 5 pagesPrelab 4Prelab 4 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2013 Register Now Prelab 4 17 pageslab8lab8 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Spring 2014 Register Now lab8 2 pagesecen 248 Prelab lab 3ecen 248 Prelab lab 3 Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2014 Register Now ecen 248 Prelab lab 3 6 pagesLab 4 ECEN 248.docxLab 4 ECEN 248.docx Texas A&M University INTRO TO DIGITAL LOGIC

ECEN 248 – Fall 2017 Register Now Lab 4 ECEN 248.docx Prev 1 2 3 4 5 Next Recent Documents 1 pagesPre_lab_4_part_2.jpgPre_lab_4_part_2.jpg Texas A&M University Digital Logic

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

ECEN 248 – Spring 2016 Register Now Pre_lab_4_part_2.jpg 2 pagesPre-Lab 6.pdfPre-Lab 6.pdf Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now Pre-Lab 6.pdf 1 pagesLab_7 (Pre_Lab).pdfLab_7 (Pre_Lab).pdf Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now Lab_7 (Pre_Lab).pdf 4 pagesLab_2.pdfLab_2.pdf Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now Lab_2.pdf 4 pagesPreLab 10.pdfPreLab 10.pdf Texas A&M University Digital Logic

ECEN 248 – Spring 2016 Register Now PreLab 10.pdf Textbook Exercises Fundamentals of Digital Logic with VHDL Design image Fundamentals of Digital Logic with VHDL Design Ch 2, Section EoC End of Chapter, Exercise 2.1Consider the expression x+yz=(x+y)(x+z) .

Consider the left handed term is x+yz and the right…Fundamentals of Digital Logic with VHDL Design Ch 3, Section EoC End of Chapter, Exercise 3.1For a 3 input logic circuit, there are 8 different combinations for which the output can be…

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

Fundamentals of Digital Logic with VHDL Design Ch 4, Section EoC End of Chapter, Exercise 4.1Write the truth table for the given function f(x_1,x_2,x_3)=\sum m(1,2,3,5) . Determine the number…Fundamentals of Digital Logic with VHDL Design Ch 5, Section EoC End of Chapter, Exercise 5.1

All positive numbers are called unsigned numbers. The binary number is represented by using the…Fundamentals of Digital Logic with VHDL Design Ch 6, Section EoC End of Chapter, Exercise 6.1Draw a 3 to 8 binary decoder for the given function, f(w_1, w_2, w_3)=\sum m(0, 2, 3, 4, 5, 7) .

It…Fundamentals of Digital Logic with VHDL Design Ch 7, Section EoC End of Chapter, Exercise 7.5Consider the characteristic table of D flip-flop is shown in Table 1. …Fundamentals of Digital Logic with VHDL Design Ch 8, Section EoC End of Chapter, Exercise 8.4The inputs are clock and reset.

The output is z and it consists of 4 bits. According to the states…Fundamentals of Digital Logic with VHDL Design Ch 9, Section EoC End of Chapter, Exercise 9.1Consider that w_{1} and w_{2} are the inputs, y_{1} and y_{2} are the next states, z_{1} and z_{2}…

Fundamentals of Digital Logic with VHDL Design Ch 10, Section EoC End of Chapter, Exercise 10.1The modified shift register circuit in which the parallel-load operation can be performed only when…Fundamentals of Digital Logic with VHDL Design INTRO TO DIGITAL LOGIC

ECEN 248 ECEN248 Lab 9: Counters Clock Dividers and Debounce Circuits – Texas A&M

Tests Questions & Answers Showing 1 to 8 of 26 View all Please see attachments for details 1 2 3 4 5 Please see an attachment for details 1 2 3 4 5 Please see an attachment for details 1 2 3 4 5

Please see an attachment for details 1 2 3 4 5 The attached problems please 1 2 3 4 5 The three attached problems. 1 2 3 4 5 These are simplified equations using boolean algebra can you please help me optimize each one and draw the circuits please. 1 2 3 4 5 Can you please help me simplify each one separately using boolean algebra 1 2 3 4 5

Back to Department Related Courses ECEN 325 – ELECTRONICS (1520 Documents)ECEN 214 – ELECTRICAL CIRCUIT THEORY (1483 Documents)ECEN 350 – COMPUTER ARCHITECTURE (1012 Documents)ECEN 314 – SIGNALS AND SYSTEMS (775 Documents)

ECEN 215 – labs (757 Documents)ECEN 449 – Microprocessor Systems (575 Documents)ECEN 303 – probability (551 Documents)ECEN 454 – DIGITAL INTEGRATED CIRCUIT DESIGN (401 Documents)ECEN 322 – (365 Documents)ECEN 370 – ELECTRICAL PROPERTIES OF MATERIALS (306 Documents)